# AMSTRAD CPC CRTC COMPENDIUM

LOGON SYSTEM

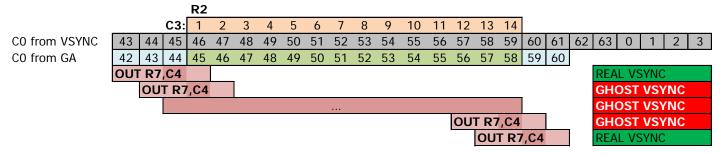

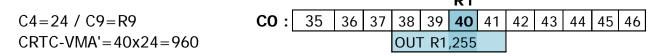

This document is licensed under a CC BY-NC-ND 4.0 license Attribution-Non Commercial-NoDerivatives 4.0 International <a href="https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode">https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode</a>

# **SOMMAIRE**

| SOMMAIRE                              | 2  |

|---------------------------------------|----|

| 1 PRÉAMBULE                           | 9  |

| 2 HISTORIQUE                          | 10 |

| 3 GÉNÉRALITÉS                         | 11 |

| 3.1 TERMINOLOGIE                      | 11 |

| 3.2 ACRONYMES                         | 12 |

| 4 CRTC & CPC                          | 13 |

| 4.1 GÉNÉRALITÉS                       | 13 |

| 4.2 NUMÉROTATION DES CRTC             | 15 |

| 4.3 VUE GENERALE DES REGISTRES        | 19 |

| 4.4 ACCES AU CRTC                     | 19 |

| 4.5 DELAIS D'ACCES                    | 22 |

| 5 LES AUTRES CIRCUITS                 | 23 |

| 5.1 ACCÈS                             | 23 |

| 5.2 CPC + / GX 4000                   | 24 |

| 6 CONSTRUCTION D'UN ÉCRAN             | 25 |

| 6.1 LOGIQUE GENERALE                  | 25 |

| 6.1.1 COMPTAGE DES CARACTERES         | 25 |

| 6.1.2 SYNCHRONISATIONS                | 25 |

| 6.1.3 AFFICHAGE DES CARACTERES        | 25 |

| 6.1.4 POINTEUR VIDEO                  | 26 |

| 6.1.5 REPRÉSENTATION SCHÉMATIQUE      | 26 |

| 7 SYNCHRONISATION                     | 29 |

| 7.1 PRINCIPES                         | 29 |

| 7.2 SYNCHRONISATION VSYNC             | 30 |

| 7.3 FAKE VSYNC                        | 33 |

| 8 AFFICHAGE, Z80A & GATE ARRAY        | 35 |

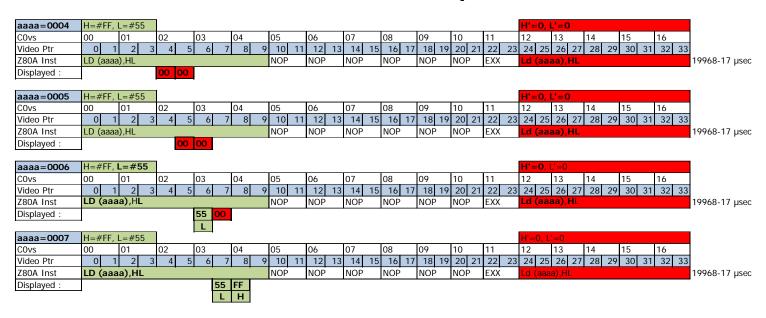

| 8.1 INSTRUCTION LD(HL),reg8 (2 µsec)  | 35 |

| 8.2 INSTRUCTION LD (aaaa),HL (5 µsec) | 35 |

| 8.3 INSTRUCTION PUSH reg16 (4 µsec)   | 36 |

| 9 GATE ARRAY                          | 37 |

| 9.1 PIXELISATION                      | 37 |

| 9.2 INKERISATION                      | 39 |

| 9.3 VITESSE DE PRISE EN COMPTE        | 39 |

| 9.4 MODE GRAPHIQUE                    | 41 |

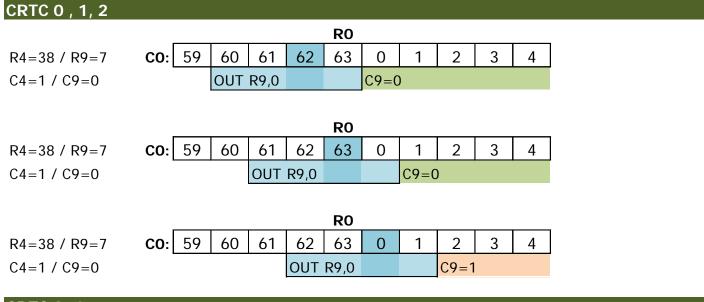

| 10 COMPTAGES : REGISTRE R9            | 43 |

| 10.1    | GÉNÉRALITÉS                                          | . 43 |

|---------|------------------------------------------------------|------|

| 10.2 E  | DELAIS DE PRISE EN COMPTE                            | 44   |

| 10.3 F  | REGLES DE COMPTAGE                                   | . 44 |

| 10.3.1  | CRTC 0                                               | 45   |

| 10.3.2  | CRTC 1                                               | . 46 |

| 10.3.3  | CRTC 2                                               | 46   |

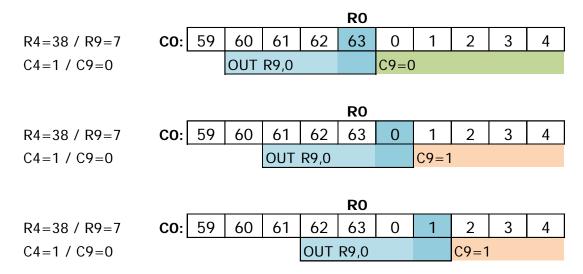

| 10.3.4  | CRTC 3, 4                                            | . 47 |

| 11 COMI | PTAGES : REGISTRE R5                                 | . 50 |

| 11.1    | GÉNÉRALITÉS                                          | . 50 |

| 11.2 C  | COMPTAGE EN AJUSTEMENT VERTICAL                      | . 51 |

| 11.2.1  | GÉNÉRALITÉS                                          | . 51 |

| 11.2.2  | CRTC 0                                               | . 51 |

| 11.2.3  | CRTC 1, 2                                            | . 52 |

| 11.2.4  | CRTC 3, 4                                            | . 52 |

| 11.3 N  | IISE A JOUR DE R5 DURANT UN AJUSTEMENT               | . 52 |

| 11.4 P  | PRISE EN COMPTE AJUSTEMENT                           | . 53 |

| 11.5 A  | JUSTEMENTS EN FOLIE                                  | . 53 |

| 11.6 R  | R6 ET AJUSTEMENT VERTICAL                            | . 53 |

| 11.7 A  | JUSTEMENT INTERLACIQUE                               | . 54 |

| 12 COMI | PTAGES : REGISTRE R4                                 | . 55 |

| 12.1    | GÉNÉRALITÉS                                          | . 55 |

| 12.2 C  | CRTC 0                                               | . 55 |

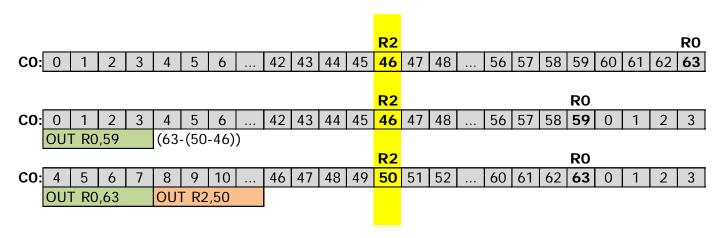

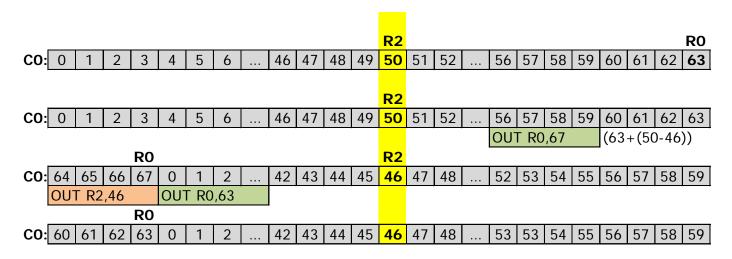

| 12.2.1  | CAS PRATIQUE: RUPTURE LIGNE A LIGNE (R.L.A.L.)       | . 56 |

| 12.3 C  | CRTC 1                                               | . 57 |

| 12.4 C  | CRTC 2                                               | . 58 |

| 12.4.1  | CAS PRATIQUE: RUPTURE LIGNE A LIGNE (R.L.A.L.)       | . 58 |

|         | CRTC 3, 4                                            |      |

| 13 COMI | PTAGES: REGISTRE R0                                  | 62   |

| 13.1    | GÉNÉRALITÉS                                          | 62   |

| 13.2 C  | CRTC 0                                               | . 63 |

| 13.2.1  | CAS PRATIQUE: R0=1                                   | 65   |

| 13.2.2  | CAS PRATIQUE: R0=0                                   | . 66 |

| 13.2.3  | CAS PRATIQUE: RUPTURE VERTICALE LAST LINE (R.V.L.L.) | . 68 |

|         | RTC 1                                                |      |

| 13.3.1  | CAS PRATIQUE: RUPTURE VERTICALE INVISIBLE (R.V.I.)   | . 71 |

| 13.4    | CRTC 2                                               | . 75 |

| 13.4.1  | CAS PRATIQUE: RUPTURE VERTICALE LAST LINE (R.V.L.L.) | . 76 |

|         | CRTC 3, 4                                            |      |

|         |                                                      |      |

| 13.6   | MI: | se a jour de ro                     | 78  |

|--------|-----|-------------------------------------|-----|

| 13.6.  | .1  | DÉLAIS DE PRISE EN COMPTE           | 78  |

| 13.6.  | .2  | EXCEPTIONS                          | 80  |

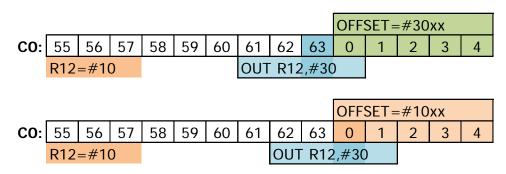

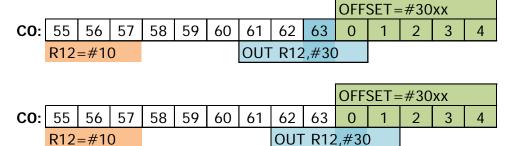

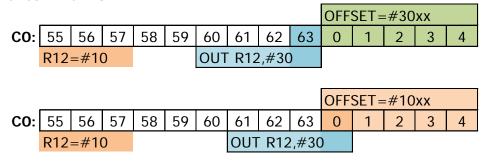

| 13.7   | OF  | FSET SELON CO                       | 81  |

| 13.7.  | .1  | ECRANS de 4 µsec (R0=3)             | 82  |

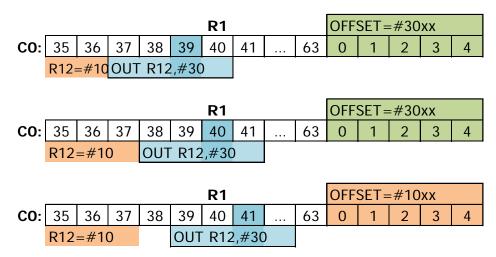

| 13.7.  | .2  | ECRANS de 2 µsec (R0=1)             | 83  |

| 13.7.  | .3  | ECRANS de 1 µsec (R0=0)             | 84  |

| 14 SYI | NCH | ROS : REGISTRE R3                   | 85  |

| 14.1   | GÉ  | NÉRALITÉS                           | 85  |

| 14.2   | LO  | NGUEUR VSYNC                        | 86  |

| 14.3   | HS  | YNC GATE ARRAY VERSUS CRTC          | 86  |

| 14.4   | HS  | YNC ET POSITION ECRAN               | 86  |

| 14.5   | HS  | YNC ET INTERRUPTIONS                | 87  |

| 14.6   | MI: | SE A JOUR DE R3 DURANT LA HSYNC     | 87  |

| 14.6.  | .1  | CRTC 0, 2                           | 88  |

| 14.6.  | .2  | CRTC 1                              | 89  |

| 14.6.  | .3  | CRTC 3, 4                           | 90  |

| 14.7   | AB  | SENCE DE HSYNC                      | 91  |

| 14.8   | DE  | MARRAGE HSYNC                       | 91  |

| 14.8.  | .1  | CRTC 0, 1, 2                        | 91  |

| 14.8.  | .2  | CRTC 3, 4                           | 91  |

| 15 SYI | NCH | ROS : REGISTRE R7                   | 93  |

| 15.1   | GÉ  | NÉRALITÉS                           | 93  |

| 15.2   | СО  | NDITIONS DE PRISE EN COMPTE         | 93  |

| 15.2.  | .1  | CRTC 0                              | 93  |

| 15.2.  | .2  | CRTC 1                              | 94  |

| 15.2.  | .3  | CRTC 2                              | 94  |

| 15.2.  | .4  | CRTC 3, 4                           | 94  |

| 15.3   | LE  | BON MOMENT                          | 95  |

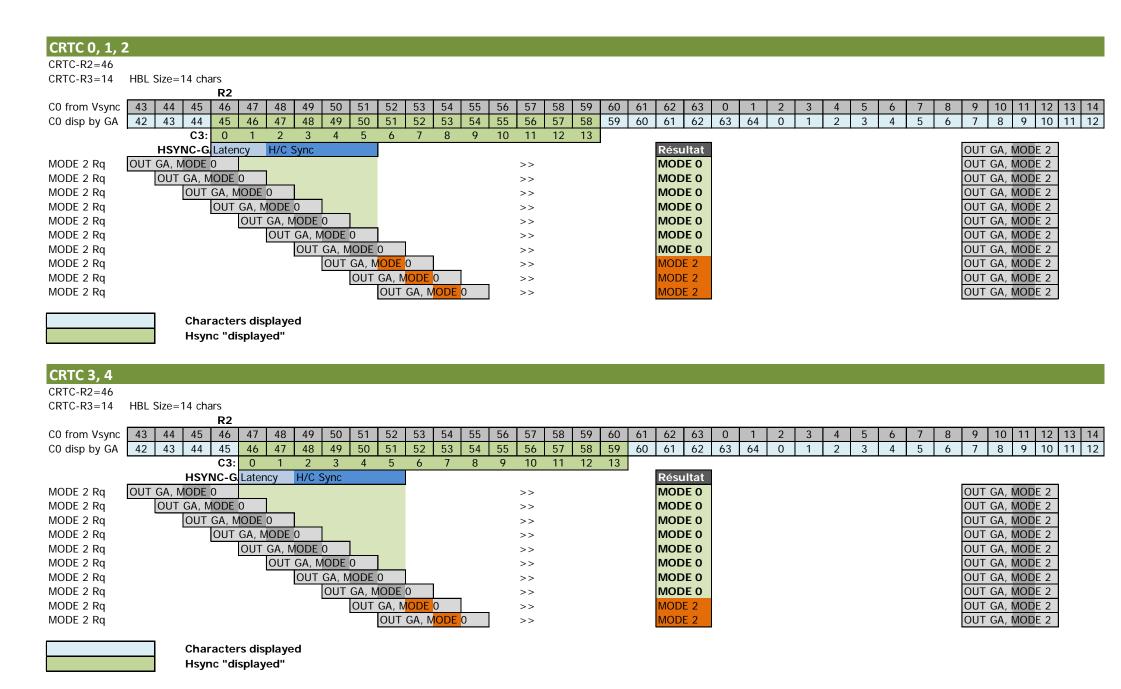

| 16 SYI | NCH | ROS : REGISTRE R2                   | 96  |

| 16.1   | GÉ  | NÉRALITÉS                           | 96  |

| 16.2   | HS  | YNC LORSQUE R2 EST PRÉDÉFINI        | 98  |

| 16.3   | MI: | SE A JOUR DE R2 DURANT LA HSYNC     | 98  |

| 16.4   | PR  | ISE EN COMPTE VSYNC DURANT LA HSYNC | 102 |

| 16.4.  | .1  | GÉNÉRALITÉS                         | 102 |

| 16.4.  | .2  | CRTC 0, 1                           | 102 |

| 16.4.  | .3  | CRTC 3, 4                           |     |

| 16.4.  | .4  | CRTC 2                              |     |

|        |     |                                     |     |

| 16.5 DIS  | SPEN ET HSYNC                                     | 105 |

|-----------|---------------------------------------------------|-----|

| 16.5.1    | CRTC 0, 1, 3, 4                                   | 105 |

| 16.5.2    | CRTC 2                                            | 105 |

| 16.6 LE   | BON MOMENT                                        | 105 |

| 16.6.1    | Passer de R2=46 à R2=50 sur des lignes de 64 µsec | 106 |

| 16.6.2    | Passer de R2=50 à R2=46 sur des lignes de 64 µsec | 106 |

| 17 AFFICH | IAGE: REGISTRE R1                                 | 107 |

| 17.1 GÉ   | NÉRALITÉS                                         | 107 |

| 17.2 AFI  | FICHAGES SELON R1                                 | 109 |

| 17.2.1    | AFFICHAGE AVEC R1 <= R0                           | 109 |

| 17.2.2    | AFFFICHAGE AVEC R1 > R0                           | 110 |

| 17.3 MIS  | SE JOUR DYNAMIQUE DE R1                           | 111 |

| 17.4 VM   | A'/VMA LORSQUE C4=0                               | 114 |

| 17.4.1    | CRTC 0, 3, 4                                      | 114 |

| 17.4.2    | CRTC 1                                            | 114 |

| 17.4.3    | CRTC 2                                            | 115 |

| 17.5 PR   | ISE EN COMPTE R1=0                                | 116 |

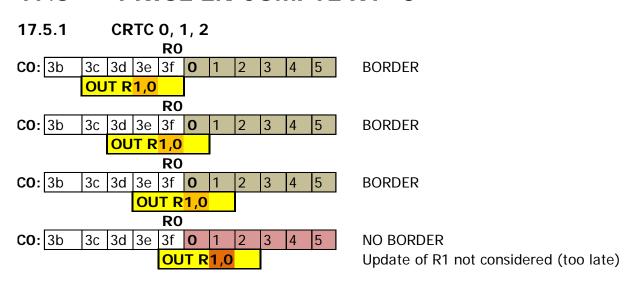

| 17.5.1    | CRTC 0, 1, 2                                      | 116 |

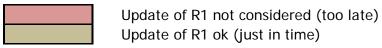

| 17.5.2    | CRTC 3, 4                                         | 116 |

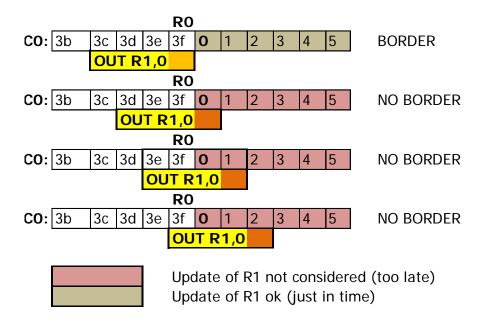

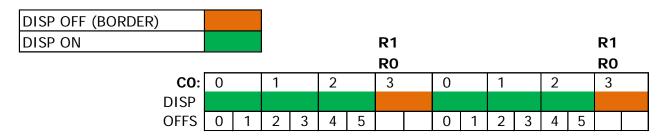

| 17.6 BO   | RDER INTERLIGNE                                   | 117 |

| 17.6.1    | R1=R0 ET C0=R0                                    | 117 |

| 17.6.2    | R1>R0 ET C0=R0                                    | 117 |

| 18 AFFICH | IAGE: REGISTRE R6                                 | 119 |

| 18.1 GÉ   | NÉRALITÉS                                         | 119 |

| 18.2 DÉ   | LAIS ET PRIORITÉS DE BORDER R6                    | 119 |

| 18.2.1    | GÉNÉRALITÉS                                       | 119 |

| 18.2.2    | CRTC 0, 2                                         | 119 |

| 18.2.3    | CRTC 1                                            | 120 |

| 18.2.4    | CRTC 3, 4                                         | 120 |

| 18.3 CO   | NFLITS R6                                         | 120 |

| 18.3.1    | GÉNÉRALITÉS                                       | 120 |

| 18.3.2    | CRTC 0, 2                                         | 121 |

| 18.3.3    | CRTC 1                                            | 122 |

| 18.3.4    | CRTC 3, 4                                         | 122 |

| 19 AFFICH | IAGE: REGISTRE R8                                 | 123 |

| 19.1 GÉ   | NÉRALITÉS                                         | 123 |

| 19.2 FO   | NCTIONS « SKEW-DISPTMG »                          | 124 |

| 19.2.1    | CRTC 0, 3, 4                                      | 124 |

|           |                                                   |     |

| 19.2.2    | CAS PRATIQUE: DESINTEGRATION DU BORDER SUR CRTC 0 | 125 |

|-----------|---------------------------------------------------|-----|

| 19.3 FO   | NCTIONS INTERLACE                                 | 127 |

| 19.3.1    | GÉNÉRALITÉS                                       | 127 |

| 19.3.2    | LES DEUX MODES INTERLACE                          | 128 |

| 19.3.3    | RESTRICTIONS                                      | 130 |

| 19.3.4    | FONCTION MAL AIMÉE                                | 130 |

| 19.4 PR   | OGRAMMATION VERTICALE EN INTERLACE                | 131 |

| 19.4.1    | CRTC 0                                            | 131 |

| 19.4.2    | CRTC 1                                            | 132 |

| 19.4.3    | CRTC 2                                            | 132 |

| 19.5 CO   | MPTAGES EN INTERLACE VIDEOMODE                    | 133 |

| 19.5.1    | CRTC 0                                            | 133 |

| 19.5.2    | CRTC 1                                            | 136 |

| 19.5.3    | CRTC 2                                            | 139 |

| 19.5.4    | CRTC 3, 4                                         | 143 |

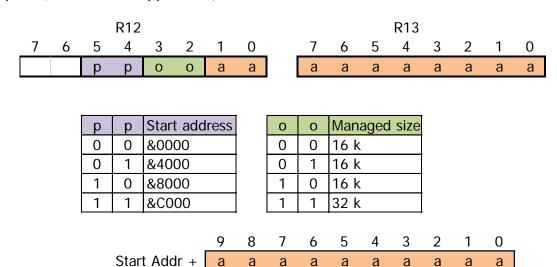

| 20 POINTI | EUR VIDEO:REGISTRES R12/R13                       | 148 |

| 20.1 GÉ   | NÉRALITÉS                                         | 148 |

| 20.2 CA   | LCUL DU POINTEUR VIDÉO                            | 148 |

| 20.3 CO   | NDITIONS DE MISE A JOUR                           | 149 |

| 20.3.1    | CRTC 0                                            | 149 |

| 20.3.2    | CRTC 1                                            | 149 |

| 20.3.3    | CRTC 2                                            | 150 |

| 20.3.4    | CRTC 3 & 4                                        | 150 |

| 20.4 DE   | LAIS DE PRISE EN COMPTE                           | 150 |

| 20.5 OV   | ERSCAN-BITS ;-)                                   | 151 |

|           | TRES EN LECTURE                                   |     |

| 21.1 GÉ   | NÉRALITÉS                                         | 152 |

| 21.2 LE   | CTURE DU CONTENU DES REGISTRES                    | 152 |

| 21.2.1    | CRTC 0                                            | 152 |

| 21.2.2    | CRTC 1, 2                                         |     |

| 21.2.3    | CRTC 3, 4                                         |     |

| 21.3 LE   | CTURE DES STATUS                                  | 153 |

| 21.3.1    | GÉNÉRALITÉS                                       | 153 |

| 21.3.2    | CRTC 0, 2                                         | 153 |

| 21.3.3    | CRTC 1                                            |     |

| 21.3.4    | CRTC 3, 4                                         |     |

|           | MMY REGISTER                                      |     |

|           | CREEN & CENTRAGE                                  |     |

|           |                                                   |     |

| 2  | 2.1   | PRÉ   | ÉAMBULE                              | 157 |

|----|-------|-------|--------------------------------------|-----|

| 2  | 2.2   | FUL   | LSCREEN HORIZONTAL                   | 158 |

| 2  | 2.3   | FUL   | LSCREEN VERTICAL                     | 158 |

| 23 | TRI   | JCS   | ET ASTUCES                           | 159 |

| 2  | 3.1   | MIS   | SE A JOUR DE R12/R13                 | 159 |

| 2  | 3.2   | UTI   | LISATION COMMUNE DE REGISTRE(S)      | 159 |

| 2  | 3.3   | ATT   | TENTE DE VSYNC                       | 160 |

| 2  | 3.4   | VAL   | EUR 0                                | 160 |

| 2  | 3.5   | OU    | TI/OUTD ET REGISTRE D'ETAT           | 161 |

| 2  | 3.6   | ITÉ   | RATIONS ET BRANCHEMENT CONDITIONNELS | 161 |

| 2  | 3.7   | PER   | RDRE DU TEMPS                        | 162 |

| 24 | DU    | REE   | INSTRUCTIONS Z80A SUR CPC            | 163 |

| 25 | INT   | ERR   | UPTIONS                              | 165 |

| 2  | 5.1   | GEN   | NERALITES                            | 165 |

| 2  | 5.2   | GES   | STION DU COMPTEUR R52                | 165 |

| 2  | 5.3   | COI   | NDITIONS DE DÉCLENCHEMENT            | 165 |

| 2  | 5.4   | INT   | ERRUPTION MODE 1                     | 166 |

| 2  | 5.5   | INT   | ERRUPTION MODE 2                     | 167 |

| 2  | 5.6   | CRT   | TC & INTERRUPTIONS                   | 167 |

|    | 25.6. | 1     | GÉNÉRALITÉS                          | 167 |

|    | 25.6. | 2     | CRTC 0, 1, 2                         | 168 |

|    | 25.6. | 3     | CRTC 0, 1                            | 168 |

|    | 25.6. | 4     | CRTC 2                               | 168 |

|    | 25.6. | 5     | CRTC 3, 4                            | 169 |

|    | 25.6. |       | MISE EN PERSPECTIVE                  |     |

| 26 | IDE   | ENTII | FICATION CRTC                        | 170 |

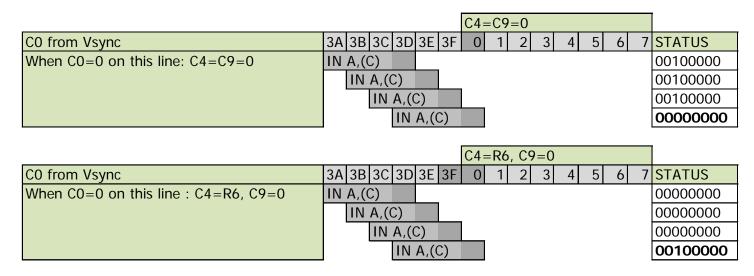

|    | 26.1. | 1     | VIA LE DEBORDEMENT DE C4 ET/OU C9    | 170 |

|    | 26.1. | 2     | VIA LA GESTION VSYNC DURANT LA HSYNC | 170 |

|    | 26.1. | 3     | VIA LA PRISE EN COMPTE DE LA VSYNC   | 170 |

|    | 26.1. | 4     | VIA LA LONGUEUR DE LA VSYNC          | 170 |

|    | 26.1. | 5     | VIA LA LONGUEUR DE LA HSYNC          | 170 |

|    | 26.1. | 6     | VIA DU BORDER, VISUELLEMENT          | 171 |

|    | 26.1. | 7     | VIA LE MODE INTERLACE                | 171 |

|    | 26.1. | 8     | VIA LE REGISTRE DE STATUS &BE00      | 171 |

|    | 26.1. | 9     | VIA LE REGISTRE DE LECTURE &BF00     | 171 |

| 27 | IDE   | ENTII | FICATION CPC                         | 172 |

| 2  | 7.1   | ΜÉ    | THODES D'IDENTIFICATION              | 172 |

|    | 27.1. | 1     | ACTIVATION DES FONCTIONS ÉTENDUES    | 172 |

| 27.1.2 | BUG PPI PORT C | 172 |

|--------|----------------|-----|

| 27.1.3 | BUG PPI PORT B | 172 |

# 1 PRÉAMBULE

L'objectif de ce document est d'apporter des informations détaillées sur le fonctionnement des différents circuits CRTC 6845 implémentés dans les CPC créés par AMSTRAD. Le CRTC est un circuit contrôleur capable de fournir une interface entre des micro-ordinateurs et des écrans cathodiques gérant un balayage vidéo.

Ce document aborde également le fonctionnement de quelques circuits associés aux CRTC, notamment le GATE ARRAY.

Ces informations peuvent servir à tout programmeur de jeu ou de démo travaillant encore sur ces machines conçues durant les années 1980-1990.

Elles peuvent aussi servir de référence à toute personne souhaitant créer un émulateur autrement qu'en adaptant son code au coup par coup pour des programmes spécifiques.

Enfin, il peut apporter des informations utiles aux utilisateurs d'autres machines équipées de CRTC similaires. Il faut cependant considérer que les timings entre le processeur, le CRTC et le circuit vidéo associé d'une autre machine peuvent modifier notablement les comportements décrits ici. Par ailleurs, ce document décrit uniquement les fonctions des CRTC utilisées sur le CPC. Le mode « texte » et le « curseur » ne sont donc pas traités.

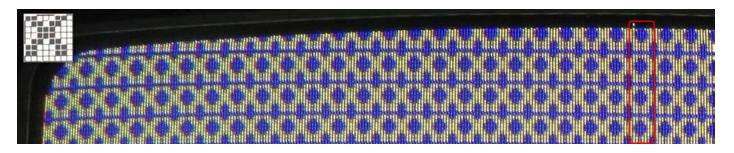

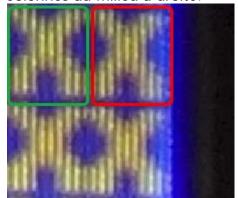

Une partie des informations indiquées dans ce document a été vérifiée à partir d'un programme de benchmark appelé SHAKER. Il a été testé pour chaque CRTC sur plusieurs machines.

Un autre document annexe contient, pour différents tests, les écrans obtenus avec l'émulateur WINAPE avec les photos d'écran pour les CRTC connus à ce jour sur CPC. Lorsqu'il n'y a pas de photo, c'est que l'émulateur n'est pas en mesure d'émuler le CRTC sans perte de synchronisation.

La vérité tient peu de place, mais l'erreur occupe une infinité de lieux. Ce document est amené à être corrigé et à évoluer.

Serge Querné Longshot / Logon System serge.querne@logonsystem.fr

#### Remerciements

Arnaud STORQ (*NoRecess*) pour son infinie patience et ses talents cachés de cameraman pour m'envoyer les résultats de SHAKER lorsque mes CPC étaient inaccessibles.

Claire DUPAS (*Cheshirecat*) pour son retour d'expérience sur les HSYNC et ses idées parfois pas si farfelues que ça :-)

Relecture molle : Sébastien BROUDIN (*Candy*)

# 2 HISTORIQUE

| Version | Date       | Mise à jour                                                                                                                                                  |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 01/01/2021 | Création du document                                                                                                                                         |

| 1.1     | 15/12/2021 | Réimport des schémas. Correctifs § 4.3, 4.5, 7.2. Regroupement status sous § 21 avec ajout des registres en lecture et définition des status des CRTC 3 & 4. |

This document is licensed under a CC BY-NC-ND 4.0 license Attribution-Non Commercial-NoDerivatives 4.0 International

# **3 GÉNÉRALITÉS**

## 3.1TERMINOLOGIE

Le CRTC est un circuit qui passe son temps à compter et à comparer.

Il contient donc principalement des compteurs dont la valeur limite est en général définie dans les registres programmables du circuit.

Dans l'objectif de construire des écrans composés de plusieurs caractères verticaux, eux mêmes constitués plusieurs lignes verticales, elles-mêmes composées de plusieurs caractères horizontaux, certaines terminologies sont associées à ces registres et compteurs.

Il est ainsi question de « *Nombre total horizontal de caractères* », « *Nombre total vertical de caractères* » ou encore « *Raster Maximum* » pour définir la valeur de certains registres, avec parfois quelques différences entre les documentations techniques. Certains émulateurs utilisent des acronymes « non officiels » pour définir le nom des compteurs associés : HCC, VTAC, VLC, VCC,... pour n'en citer que quelques uns.

Ces terminologies ne sont plus du tout adaptées lorsqu'on travaille à un niveau différent de celui prévu pour la construction d'un écran « standard ».

En effet, à un certain niveau, il n'y a plus vraiment de logique de comptage « horizontale » ou « verticale », et il est donc difficile de parler de « caractères » sans se prendre les pieds dans le tapis, car selon la programmation du circuit, un caractère vertical peut aussi être un caractère horizontal.

Cette notion existe tout au plus par rapport à la logique de synchronisation de l'écran construit.

Etant donné qu'il est possible de réduire la taille d'une ligne à 1 µsec, de réduire la taille d'un caractère vertical à 1 ligne et réduire la taille d'un écran à 1 caractère, les appellations horizontales et verticales perdent quelque peu leur sens.

C'est pourquoi dans ce document je vais en général noter les registres du CRTC sous la forme **Rn** et les compteurs associés par **Cn**. Lorsqu'il sera question de « caractères », il s'agira des mots traités par la GATE ARRAY à partir de l'adresse fournie par le CRTC. J'ai nommé VMA et VMA' les deux pointeurs internes du CRTC.

J'invite les auteurs d'émulateurs se basant sur ce document à adopter ces notations. Voici une équivalence de quelques termes rencontrés :

| Noms identifiés dans certains émulateurs | Compteur                   |  |  |  |  |  |  |

|------------------------------------------|----------------------------|--|--|--|--|--|--|

| HCC (Horizontal Char Counter)            | CO                         |  |  |  |  |  |  |

| VLC (Vertical Line Counter)              | C9                         |  |  |  |  |  |  |

| VCC (Vertical Character Counter)         | C4                         |  |  |  |  |  |  |

| VSC (Vertical Sync Counter)              | C3h                        |  |  |  |  |  |  |

| HSC (Horizontal Sync Counter)            | C3I                        |  |  |  |  |  |  |

| VTAC (Vertical Total Adjust Counter)     | C5 or C9 (on CRTC 0)       |  |  |  |  |  |  |

| VMA (byte pointer)                       | VMA or VMA' (word pointer) |  |  |  |  |  |  |

## 3.2ACRONYMES

**CRTC:** Cathod Ray Tube Controller: Circuit qui permet d'interfacer un ordinateur avec un moniteur cathodique capable de gérer des lignes raster.

**VSYNC**: Vertical SYNC : Se dit du signal émis par le CRTC qui permet au moniteur (via le GATE ARRAY sur CPC) de synchroniser l'écran verticalement.

**VBL**: Vertical BLank: Se dit de la période durant laquelle le canon à électron du moniteur, qui a atteint le bas de l'écran, désactive le faisceau pour revenir en haut de l'écran.

**HSYNC**: Horizontal SYNC: Se dit du signal émis par le CRTC qui permet au moniteur (via le GATE ARRAY sur CPC) de synchroniser l'écran horizontalement.

**HBL**: Horizontal BLank: Se dit de la période durant laquelle le canon à électron du moniteur, qui a atteint le côté droit du moniteur, désactive le faisceau pour revenir à gauche de l'écran.

**VMA :** Video Memory Address : Pointeur CRTC sur les mots adressés en mémoire et fourni au GATE ARRAY pour l'affichage.

**ASIC:** Application Specific Integrated Circuit: Se dit d'un circuit conçu pour une application spécifique. Le GATE ARRAY est un ASIC.

**RLAL**: Rupture Ligne à Ligne : Se dit d'une rupture horizontale ou l'adresse est changée sur chaque ligne raster de l'écran.

**RV**: Rupture Verticale : Se dit d'une rupture dont l'axe n'est pas « horizontal », et qui permet de créer des zones horizontalement.

**RVI**: Rupture Verticale Invisible: Se dit de ruptures verticales ayant lieu durant la Hsync et non visibles.

**RVLL**: Rupture Verticale Last Line : Se dit de ruptures exploitant le traitement « dernière ligne » de C4 des CRTC 0 et 2.

## 4 CRTC & CPC...

## 4.1GÉNÉRALITÉS

Sur AMSTRAD CPC, la durée d'un caractère CRTC est de 1 µsec.

Ce caractère CRTC représente 2 octets en mémoire.

Le pointeur mémoire est communiqué par le CRTC au GATE ARRAY, **qui va toujours lire la** "ram centrale" de 64k. Le GATE ARRAY ne peut pas lire les données en ROM ou dans la RAM additionnelle des 6128 (ou des extensions mémoire), sauf intervention de Tot0.

Le CRTC est programmé de manière à ce que l'image ainsi créée soit supportée par un moniteur. Un raccourci de langage consiste à utiliser le terme NOP au lieu de µsec (microseconde) car c'est le temps pris par cette instruction en Z80A.

Sur CPC, les instructions Z80A sont alignées en arrondissant les cycles M d'une instruction sur un multiple de 4 cycles T. Cet alignement est lié à la nécessité pour le GATE ARRAY d'interrompre le Z80A pour accéder à la ram dont l'adresse est fournie par le CRTC. Ce fonctionnement ralentit certaines instructions par rapport à la fréquence d'horloge. Réaliser un code précis nécessite de connaître le temps exact pris par chaque instruction. Voir chapitre 23, page 163, pour le détail de ces durées pour chaque instruction.

#### Un peu d'histoire

Les moniteurs et téléviseurs cathodiques sont contraints d'aligner leur fréquence d'affichage au réseau de distribution d'électricité du pays de commercialisation.

En Europe notamment, les téléviseurs construits pour supporter les formats SECAM et PAL fonctionnent avec une fréquence horizontale de 15.625Khz, pour une fréquence verticale de 50Hz.

A noter que le format Américain (et Japonais) était le NTSC (National Television System Committee) avec une fréquence horizontale de 17.734Khz et verticale de 60Hz.

La fréquence horizontale de 15.625Khz est issue de l'utilisation de ligne à retard de 64 µs, inventée pour la conception du format Secam par l'ingénieur Henri de France. Pour rappel, 64µs = 0.000064 seconde (juste le temps de prendre un café serré).

Le CRTC suit cette logique et traite 1 million de caractères par seconde environ car sa fréquence est de 1 Mhz.

Sans intervention diabolique sur la position de la HSYNC, il est en principe programmé pour générer des lignes complètes de 64 µsec.

Pour se rapprocher de la fréquence voulue, le CRTC est en général programmé pour afficher 312 lignes de 64µs, soient très exactement 19968 µsec (0.019968 secondes).

Cette fréquence étant liée à une horloge, on peut constater des dérives entre 2 machines au bout d'un certain temps.

Le format standard initialisé par la ROM CPC dans un pays Européen est :

- Lignes de 64 caractères "CRTC" horizontaux de 1µs chacun (composées de 40 caractères affichés et 24 non affichés).

- 312 lignes verticales, sous divisées en caractères verticaux de 8 lignes, soient 39 caractères.

- Formule : ((R4+1) x (R9+1)) + R5

- Sur ces 39 lignes de caractères, 25 sont affichées.

- Adresse en ROM de la table CRTC: &5C5

Le format standard initialisé par la ROM CPC aux Etats-Unis est :

- Lignes de 64 caractères "CRTC" horizontaux de 1µs chacun (composées de 40 caractères affichés et 24 non affichés).

- 262 lignes verticales, sub divisées en caractères verticaux de 8 lignes, soient 32 caractères + 6 lignes d'ajustement

- Formule : ((R4+1) x (R9+1)) + R5

- Sur ces 32.75 lignes de caractères, 25 sont affichées.

- Adresse en ROM de la table CRTC : &5D5

Note: C'est le bit 4 du port B du PPI (LK4) qui permet de tester quelle table utiliser.

<u>Note</u>: L'initialisation des registres du CRTC est une des premières choses que la ROM BASSE du CPC effectue à l'allumage et au reset de la machine. L'initialisation des registres commence 64 µsec après la lecture de la première instruction en ROM par le Z80A. Les registres sont initialisés en partant du registre 15 jusqu'au registre 0.

Les moniteurs CTM utilisent les circuits PC1031 (moniteur monochrome vert GT65) et PC1378 (moniteur couleur CTM 644). Ces circuits servent à piloter le déflecteur horizontal pour produire le signal dont le canon a besoin pour le balayage.

Le GATE ARRAY du CPC produit, via son pin 5, un signal de synchronisation composite combinant la VSYNC et la HSYNC, qui arrive au connecteur DIN prévu pour le moniteur (via une résistance 220 Ohm (R137)).

Ce signal composite est décodé par les circuits (PC1031 ou PC1378) du moniteur. [Le moniteur n'étant pas un téléviseur, les signaux pour l'image sont toujours du RGB]

Le CRTC dispose de registres pour gérer un curseur et lire les données envoyées par un "stylo optique". Les registres relatifs au curseur ne servent pas sur CPC, qui ne gère pas de curseur hardware, en général prévu lorsqu'un mode texte est géré.

Ils peuvent cependant mériter un point d'intérêt, car l'action sur d'autres registres dans ou hors d'une période synchronisation, avec des petites valeurs, pourrait entrainer des conséquences sur d'autres registres.

Le fonctionnement de ces registres n'est pas abordé (pour le moment) dans ce document.

## 4.2 NUMÉROTATION DES CRTC

AMSTRAD a eu la brillante idée d'utiliser des circuits CRTC 6845 fabriqués par différents constructeurs dans ses machines. Ils ont même conçu des ASIC capables d'émuler son fonctionnement.

#### Un peu d'histoire

Alors que la société AMSTRAD voulait attaquer le marché américain avec les CPC 6128, un problème a été identifié en ROM avec la valeur du registre 5 (ajustement vertical).

Cette valeur a été fixée à 6 en conformité avec la fréquence souhaitée de 60Hz aux USA (262 lignes), mais faisait (à tort) l'impasse sur le système d'interruption géré par le GATE ARRAY. En effet, sur un CPC Européen, les interruptions débutent 2 lignes (on considèrera qu'on a 1 HSYNC par ligne) après la survenue du signal VSYNC par le CRTC.

Ces interruptions ont une période de 52 "lignes", ce qui donne exactement 6 périodes durant les 312 lignes (voir chapitre 25.6 sur les INTERRUPTIONS). Pour caler 5 périodes de 52 lignes, il aurait fallu programmer 260 lignes et non 262 comme cela a été fait, et donc que R5 soit programmé avec 4 au lieu de 6.

Ces 2 lignes de plus provoquent l'arrivée de l'interruption sur la même ligne que celle sur laquelle le CRTC signale le début de la VSYNC, MAIS <u>avant lui</u>.

Autrement dit, sur un CPC américain, un programme dont le code principal teste l'attente VSYNC via le PPI peut être interrompu pendant cette attente. Si l'interruption dure trop longtemps, à son retour, la boucle d'attente de la VSYNC a loupé le signal (le bit est revenu à 0), et un risque de "deadlock" existe.

Cela pouvait engendrer des problèmes de compatibilité pour des programmes produits en Europe. AMSTRAD a alors décidé de remédier au problème en ....modifiant la table 60 Hz en ROM.... Non...je plaisante...trop simple.

Pour éviter ce « deadlock » sans modifier la ROM, les ingénieurs Amstrad se sont dit qu'ils pouvaient "limiter le problème" en augmentant la durée de la VSYNC. C'était parfaitement possible en utilisant le registre 3 du CRTC, qui avait été programmé avec 8 lignes ..... dans la ROM.

Il est probable qu'ils se soient dit qu'il existait des modèles de CRTC dépourvus de la fonction utilisée pour fixer le nombre de lignes de la VSYNC (ces modèles fixent le nombre de lignes à 16) et décidé ainsi que les CPC américains ne seraient équipés que de CRTC 1 et 2, dépourvus de cette fonction.

Si les ingénieurs AMSTRAD étaient conscients de l'existence de ces différences, on peut supposer que les premiers CRTC utilisés étaient des types 0, puisque cette fonction est utilisée et programmée par la ROM.

De là à pouvoir affirmer que sans un bug lié à un 4 à la place d'un 6 dans la ROM, il n'y aurait qu'un seul type de CRTC utilisé dans tous les CPC, c'est faire fi des considérations commerciales sur le marché des composants par rapport au succès de la machine en Europe...

Plusieurs entreprises ont créé des versions différentes du circuit, implémentant des fonctions complémentaires, comme la programmation du nombre de lignes de la VSYNC que je viens d'évoquer.

On peut cependant déduire que les concepteurs de la ROM BASIC :

- travaillaient originellement avec un CRTC disposant de la possibilité de programmer ce nombre de lignes pour la VSYNC.

- ont estimé que 8 lignes de VSYNC étaient suffisantes pour synchroniser verticalement l'image sur un moniteur CTM.

Au-delà des différences fonctionnelles et techniques documentées dans les guides constructeurs des circuits (appelés « datasheet » avec 2 « e »), ces CRTC ont tendance à se comporter différemment lorsqu'on commence à modifier des registres :

- plusieurs fois au cours du balayage.

- durant ou hors des périodes HSYNC/VSYNC.

- avec la valeur 0, qui est un cas particulier pour la gestion de plusieurs registres.

Ces différences impactent la compatibilité des programmes, notamment lorsqu'il est question de modifier l'adresse du pointeur vidéo en cours de balayage.

Cette technique est encore appelée communément "*Rupture*" car... elle est plus simple et générique à dire que "*Offset Split Screen*".

Les différences de gestion des compteurs (qui peuvent déborder dans quelques situations) induisent généralement un défaut de synchronisation horizontale (R2) et/ou verticale (R7).

Si un code Z80A "attend" le signal VSYNC ou qu'il utilise les interruptions (qui dépendent de la HSYNC), le bordel est accentué.

#### Un peu d'histoire

A ma connaissance, le premier programme a avoir réalisé un test de CRTC est le jeu "Crafton & Xunk" (Get Dexter), écrit par Rémi Herbulot et Michel RHO en 1986.

Dans ce jeu, le changement d'écran a lieu grâce à un scrolling horizontal, qui utilise le registre 2 (positionnement de la HSYNC sur un autre caractère).

Cette méthode, sur un CRTC MOTOROLA, provoque une perte de synchro verticale lorsque la VSYNC se produit durant une HSYNC (Ghost Vsync).

Autrement dit, dans cette situation, le CRTC croit faussement générer un signal VSYNC pour le moniteur.

Je suppose que Rémi Herbulot devait avoir accès, chez Ere Informatique, à un CPC avec un CRTC HITACHI (comme le mien à l'époque) et un autre avec un CRTC MOTOROLA.

Ayant fait ce constat, il a créé un test basé sur la lecture en &BF00 du registre 12, qui permet de distinguer le CRTC HITACHI du CRTC MOTOROLA.

Et il a donc géré un affichage avec et sans scrolling de l'écran.

C'est pourquoi il n'y a pas de scrolling également sur les CPC équipés de CRTC UMC, alors que ce CRTC le permet sans problème, car comme pour le CRTC MOTOROLA, son registre 12 n'est pas lisible.

Pour l'anecdote, j'avais retiré le test "anti scroll" sur le CPC d'un ami pour voir ce que ça donnait, et comme ça fonctionnait (il avait sans doute un CRTC 1), je me suis dit que ce test était prévu pour autre chose. J'étais alors loin de me douter que les CRTC étaient différents.

#### Un peu d'histoire (encore!)

Lorsque les premières techniques de "rupture" ont commencé à être utilisées massivement dans les démos, les différences entre CRTC ont vite commencé à poser problème.

Et notamment lorsque les programmeurs indépendants (souvent lycéens ou étudiants) ont commencé à constituer la scène « démo » et que leurs démos ont commencé à circuler de manière moins discrétionnaire. Au départ, ces premières démos étaient surtout des introductions pour des jeux craqués qui circulaient dans les cours d'école.

[ Je crois qu'il existe un jeu des années 80 qui a rencontré ce type de problème avec le CRTC (à vérifier) ]

Les premiers programmeurs de démo n'avaient pas encore constitué de "réseau" (la demoscene) et disposaient en général d'une seule machine sous la main.

Les premières intros et démos circulaient au niveau d'un cercle restreint et très régional. Le "réseau" consistait, dans les années 80, à des échanges postaux, minitels (un ancêtre français d'internet, comme prestel en UK) et des échanges téléphoniques ruineux hors des départements, avec très peu ou pas de relations avec les autres pays.

La communication avec des personnes d'autres régions est d'abord passée par la consultation de petites annonces dans les rares magazines informatiques de l'époque à en disposer, car il était difficile de trouver des coordonnées dans une introduction précédant un jeu craqué. Les programmeurs pouvaient difficilement se rendre compte du résultat produit par leur code sur d'autres machines, et l'inertie était énorme.

Il était difficile d'adapter le code via des échanges postaux, sans disposer de la machine (ou même de vouloir le faire, tout simplement).

Les problématiques rencontrées pouvaient aller de la désynchronisation d'image au plantage pur et simple de la machine.

Il était difficile d'être catégorique sur l'origine effective de ces problèmes, et surtout sur leur étendue. Néanmoins, avec le regroupement des demomakers et l'agrandissement de la demoscene, il a été possible de confronter le code sur différentes machines.

La présence de quelques électroniciens dans les rangs des demomakers a permis d'identifier les coupables... (M. SUGAR est toujours en fuite).

Quelques règles "universelles" issues de démarches empiriques ont été décrites dans des documentations secrètes qui ne le sont pas restées longtemps ("Il ne faut pas faire cette opération ici pour que ça fonctionne partout", par exemple).

A noter que certaines techniques sont toujours à l'heure actuelle considérées impossibles à réaliser d'un CRTC à l'autre (jusqu'à ce document...).

Le CRTC 2 (MOTOROLA) s'est vite avéré être celui posant problème pour une des techniques les plus utilisées, qui consiste à placer R4=R9=0.

Le code nécessaire pour assurer la compatibilité entre CRTC peut néanmoins être bien plus complexe que de juste savoir quand modifier un registre 9 ou 4, nous allons le voir...

Afin de pouvoir exploiter les règles permettant la compatibilité, il était nécessaire dans un premier temps de pouvoir identifier les différents CRTC.

De nombreuses méthodes existent aujourd'hui. Voir chapitres 26, page 170, et 27, page 172.

La numérotation est restée à ce jour celle fixée en fonction de l'ordre ou j'ai découvert ces circuits avec l'aide de quelques membres du groupe de demomakers Logon System.

Nous avons découvert le CRTC émulé "Pré ASIC" après la sortie de l'AMSTRAD PLUS, et c'est pourquoi son numéro est supérieur à 3, bien qu'il soit sorti plus tôt chronologiquement.

| Type | Marque           | Modèle     |  |  |  |

|------|------------------|------------|--|--|--|

| 0    | HITACHI          | HD6845S(P) |  |  |  |

| 0    | UMC              | UM6845     |  |  |  |

| 1    | UMC              | UM6845R    |  |  |  |

| 2    | MOTOROLA         | MC6845(P)  |  |  |  |

| 3    | AMSTRAD ASIC 404 |            |  |  |  |

| 4    | AMSTRAD          | ASIC 40226 |  |  |  |

**Note 1 :** Les CRTC 3 et 4 sont des CRTC émulés par des ASIC, mais sont néanmoins des CRTC! Sans activer les fonctions complémentaires de l'ASIC 40489, le comportement de ces deux CRTC ne peut pas être différencié actuellement.

**Note 2 :** Le "Pré-ASIC" (CRTC 4) avait très certainement été conçu dans l'optique de l'AMSTRAD PLUS, car son compteur C9 est prévu pour être interrompu sur n'importe quelle ligne. C'est pourquoi positionner R9 à 0 peut se faire sur la dernière ligne d'un caractère (compatibilité CRTC 0) ou sur la première ligne d'un caractère (compatibilité CRTC 1).

<u>Note 3 : Il n'est pas exclu, encore à l'heure actuelle, que certaines séries de CPC, soient équipés de modèles de CRTC différents, disponibles chez les 3 constructeurs. (Merci de me le rapporter si vous découvrez un autre modèle, et que vous êtes sûr que ce n'est pas votre petite sœur qui l'a remplacé pour vous faire une blague).</u>

A priori, le CRTC HD6845S de HITACHI, qui est identifié comme un type 0, se comporte exactement comme le CRTC UM6845 de UMC. Sans doute un échange de bon procédé entre les firmes ou c'est juste le marquage qui a changé...

La documentation UMC le précise dans sa table de comparaison avec les autres circuits.

Il n'y a pas à ce jour de test qui permette la distinction de ces deux circuits, mais c'est peut-être possible via le mode « Interlace » ou la gestion particulière de C0 par le HD6845S.

**Note 4 :** Programmer R3 avec &8x est une très mauvaise habitude, puisque les CRTC 1 et 2 existent aussi dans les machines Européennes, et qu'ils ne respectent pas cette valeur...

<u>Note 5 :</u> Programmer une modification précise d'un registre CRTC dans une routine d'interruption qui n'interrompt pas un code parfaitement synchronisé est une très mauvaise idée. (et peut laisser croire (à tort) à une différence de CRTC).

## 4.3 VUE GENERALE DES REGISTRES

|           |                                       |           |     |   | CRTC 0 |   |   |   |   |   |   |  |     | CRTC 1, 2 |   |     |     |   |     |   |     |   | CRTC 3, 4 |     |   |   |   |     |  |  |

|-----------|---------------------------------------|-----------|-----|---|--------|---|---|---|---|---|---|--|-----|-----------|---|-----|-----|---|-----|---|-----|---|-----------|-----|---|---|---|-----|--|--|

| Register  | Definition                            | Unit      | r/w | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  | r/w | 7         | 6 | 5 4 | 1 3 | 2 | 1   | 0 | r/v |   | 7 6       | 5   | 4 | 3 | 2 | 1 0 |  |  |

| R0        | Horizontal total character number     | Char      | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R1        | Horizontal displayed character number | Char      | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R2        | Position of horizontal sync. pulse    | Char      | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R3        | Pulse width of horizontal sync. pulse | Function  | W   | ٧ | ٧      | ٧ | ٧ | h | h | h | h |  | W   |           |   |     | h   | h | h   | h | W   | \ | / V       | ٧   | ٧ | h | h | h   |  |  |

| R4        | Vertical total character number       | Char Row  | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R5        | Total raster adjust                   | Scan Line | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R6        | Vertical displayed character number   | Char Row  | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R7        | Position of vertical sync. pulse      | Char Row  | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R8        | Interlace Mode and Skew               | Function  | W   | С | С      | d | d |   |   | i | i |  | W   |           |   |     |     |   | i i |   | W   | C | С         | d   | d |   |   | i   |  |  |

| R9        | Max Scan Line Address                 | Scan Line | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| R10       | Cursor start                          | Scan Line | W   |   | b      | p |   |   |   |   |   |  | W   |           | b | р   |     |   |     |   | r   | S | s   1     | S   | S | S | S | s s |  |  |

| R11       | Cursor end                            | Scan Line | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | r   | S | s C       | ) s | 1 | S | S | s s |  |  |

| R12       | Display start address (High)          | Pointer   | r/w |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | r/v | ٧ |           |     |   |   |   |     |  |  |

| R13       | Display start address (Low)           | Pointer   | r/w |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | r/v | ٧ |           |     |   |   |   |     |  |  |

| R14       | Cursor address (High)                 | Pointer   | r/w |   |        |   |   |   |   |   |   |  | r/w |           |   |     |     |   |     |   | r/v | ٧ |           |     |   |   |   |     |  |  |

| R15       | Cursor address (Low)                  | Pointer   | r/w |   |        |   |   |   |   |   |   |  | r/w |           |   |     |     |   |     |   | r/v | ٧ |           |     |   |   |   |     |  |  |

| R16       | Light Pen (High)                      | Pointer   | r   |   |        |   |   |   |   |   |   |  | r   |           |   |     |     |   |     |   | r   |   |           |     |   |   |   |     |  |  |

| R17       | Light Pen (Low)                       | Pointer   | r   |   |        |   |   |   |   |   |   |  | r   |           |   |     |     |   |     |   | r   |   |           |     |   |   |   |     |  |  |

| Access po | orts to the CRTC on CPC               |           | r/w | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  | r/w | 7         | 6 | 5 4 | 1 3 | 2 | 1   | 0 | r/v | N | 7 6       | 5   | 4 | 3 | 2 | 1 0 |  |  |

| &BC00     | Register selection                    | Number    | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   | 1 |   |     |  |  |

| &BD00     | Register write                        | Value     | W   |   |        |   |   |   |   |   |   |  | W   |           |   |     |     |   |     |   | W   |   |           |     |   |   |   |     |  |  |

| &BE00     | Register status                       | Function  |     |   |        |   |   |   |   |   | Ш |  | r   |           | L | b   |     |   |     |   | r   |   |           |     |   |   |   |     |  |  |

| &BF00     | Register read                         | Value     | r   |   |        |   |   |   |   |   |   |  | r   |           |   |     |     |   |     |   | r   |   |           |     |   |   |   |     |  |  |

Voir chapitres 21, 26.1.8 et 26.1.9 pour obtenir plus d'informations sur le contenu du registre de status et du registre de lecture selon les différents CRTC.

#### 4.4 ACCES AU CRTC

L'accès aux entrées/sorties avec un Z80A nécessite en général d'utiliser des instructions spécifiques.

Ces instructions (OUT, OUTI, INI, IND...) sont en principe prévues pour utiliser des périphériques dont les adresses sont définies sur les 8 bits de poids faible du bus d'adresse 16 bits.

Le bus d'adresse 16 bits est spécifié dans le registre **BC**, mais certaines instructions (OUTD, OUTI, INI, IND, ...) utilisent aussi **B** comme compteur.

Dans l'optique de conception d'un ordinateur, il n'est pas conseillé de placer l'adresse des périphériques pouvant utiliser ces instructions sur les 8 bits de poids fort du bus d'adresse.

Ce sage conseil de M. ZILOG n'a pas été écouté par M. SUGAR.

Aussi l'accès aux périphériques sur CPC passe principalement par les bits **A8..A15 du bus d'adresse**. (le FDC 765 faisant partiellement exception)

Les bits de sélection des périphériques doivent en conséquence être positionnés sur B.

#### Bienvenue sur le CPC!

| Exemples                                                    |            |                             |  |  |  |  |  |  |

|-------------------------------------------------------------|------------|-----------------------------|--|--|--|--|--|--|

| Selection registre 12                                       |            |                             |  |  |  |  |  |  |

|                                                             | BASIC      | OUT &BC00,12                |  |  |  |  |  |  |

|                                                             | Z80A       | LD BC,&BC00+12:OUT(C),C     |  |  |  |  |  |  |

|                                                             |            |                             |  |  |  |  |  |  |

| Envoi valeur &30 sur registre 12 (sélectionné précédemment) |            |                             |  |  |  |  |  |  |

|                                                             | BASIC      | OUT &BD00,&30               |  |  |  |  |  |  |

|                                                             | Z80A       | LD BC,&BD30:OUT (C),C       |  |  |  |  |  |  |

|                                                             |            |                             |  |  |  |  |  |  |

| Lecture registre 12 (séle                                   | ctionné ou | ı mise à jour précédemment) |  |  |  |  |  |  |

|                                                             | BASIC      | PRINT INP(&BF00)            |  |  |  |  |  |  |

|                                                             | Z80A       | LD BC,&BF00 : IN A,(C)      |  |  |  |  |  |  |

|                                                             |            |                             |  |  |  |  |  |  |

| Lecture registre de statu                                   | S          |                             |  |  |  |  |  |  |

|                                                             | BASIC      | PRINT INP(&BE00)            |  |  |  |  |  |  |

|                                                             | Z80A       | LD BC,&BE00 : IN A,(C)      |  |  |  |  |  |  |

|                                                             |            |                             |  |  |  |  |  |  |

L'utilisation de B condamne l'utilisation d'instructions intéressantes permettant d'envoyer ou lire des séries de valeurs successives sur un port, comme OTIR, OTDR, INIR, INDR.

En effet ces instructions utilisent B comme compteur du nombre de valeurs à lire dans une table, et décrémentent ce compteur jusqu'à atteindre la valeur 0.

#### Remarque digressive :

Ces instructions répétitives peuvent être expérimentalement utilisées, pour traiter plus d'une valeur, sur un périphérique dont les bits de sélection ne participent pas au compteur (bits "haut"), comme le GATE ARRAY.

Il est possible de lancer une de ces instructions et de l'interrompre sauvagement en la positionnant judicieusement avant qu'une interruption survienne.

Cette interruption devra néanmoins "oublier" l'adresse de retour placée sur la pile avant de ré-autoriser d'autres interruptions.

L'intérêt est cependant très limité (et surtout ludique) et pourra activer d'autres périphériques selon le nombre de valeurs lues dans la table.

Il reste néanmoins possible d'utiliser

- Les instructions OUTI ou OUTD pour envoyer une par une des données issues d'une table (pointée par HL) au CRTC.

- Les instructions INI ou IND pour lire une par une des données issues d'une table (pointée par HL) du CRTC.

L'intérêt est que ces instructions sont "rapides" au regard du nombre d'opérations effectuées.

L'utilisation de l'instruction OUTI/OUTD est possible en incrémentant préalablement B entre chaque instruction pour OUTI/OUTD car B est décrémenté avant l'accès au port.

Pour le CRTC, qui utilise les bits 0 et 1 de B comme index, cela implique que B soit pré-chargé avec l'adresse du port + 1 pour que les instructions OUTI/OUTD fonctionnent.

Pour les instructions de lecture, le périphérique adressé est défini par BC avant la décrémentation de B, qui doit donc contenir l'adresse normale du port avant lecture.

Exemple en Z80A:

LD BC,&BC02 ; Sélection registre position Hsync

OUT (C),C

LD HL, TABHSYNC ; Pointeur sur la table des positions Hsync

LD B,&BD+1 ; Port envoi donnée + 1, soit &BE

OUTI ; OUTI décrémente B, envoie TABHSYNC[0] sur le port &BD

; et incrémente le pointeur

INC B ; B est remis sur &BE

OUTI ; OUTI décrémente B, envoie TABHSYNC[1] sur le port &BD

; et incrémente le pointeur

TABHSYNC DB 50, 10

Autres instructions en Z80A permettant de traiter une entrée sortie :

| INSTRUCTIONS | DUREE  | DESCRIPTION                                                                                                                                                                                                                                                                             |

|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT (C),r8   | 4 µsec | r8=[A ou B ou C ou D ou E ou H ou L]<br>Ecriture sur les périphériques définis dans BC de la valeur contenue dans le<br>registre r8.                                                                                                                                                    |

| OUT (n),A    | 3 µsec | L'adresse d'entrée sortie est définie par le couple An, et la donnée envoyée au périphérique est A. Cette double contrainte limite drastiquement le nombre de valeurs disponibles pour un périphérique sans provoquer un effet collatéral sur un autre périphérique (sélection+valeur). |

| OUT (C),0    | 4 µsec | Ecriture sur les périphériques définis dans BC de la valeur 0.<br>Une instruction intéressante pour un demomaker! Mais pas que                                                                                                                                                          |

| IN r8,(C)    | 4 µsec | r8=[A ou B ou C ou D ou E ou H ou L] Lecture dans le registre r8 de la valeur envoyée par le périphérique défini dans BC. Si plusieurs périphériques sont sélectionnés, nul doute qu'un jeu des chaises musicales va avoir lieu                                                         |

| IN A,(n)     | 3 µsec | L'adresse d'entrée sortie est définie par le couple An, et la donnée lue va modifier A.                                                                                                                                                                                                 |

| IN (C)       | 4 µsec | C'est une instruction « non officielle »<br>La valeur présente sur le bus de données est lue et son évaluation affecte F                                                                                                                                                                |

#### 4.5DELAIS D'ACCES

Le tableau suivant indique pour quelques instructions d'écriture (moment ou le registre est effectivement mis à jour dans le circuit) et de lecture (moment ou la valeur dans le circuit est effectivement mise à jour dans le registre ou la ram).

| INSTRUCTIONS | DUREE  | PRISE EN COMPTE I/O   |

|--------------|--------|-----------------------|

| OUT (C),r8   | 4 µsec | 3 <sup>ème</sup> µsec |

| OUT (n),A    | 3 µsec | 3 <sup>ème</sup> µsec |

| OUT (C),0    | 4 µsec | 3 <sup>ème</sup> µsec |

| OUTI         | 5 µsec | 5 <sup>ème</sup> µsec |

| OUTD         | 5 µsec | 5 <sup>ème</sup> µsec |

| IN r8,(C)    | 4 µsec | 4 <sup>ème</sup> µsec |

| INI          | 5 µsec | 4 <sup>ème</sup> µsec |

| IND          | 5 µsec | 4 <sup>ème</sup> µsec |

| IN A,(n)     | 3 µsec | 3 <sup>ème</sup> µsec |

Il est toutefois important de noter que la prise en compte d'une écriture durant la microseconde de mise à jour n'a pas lieu au même « moment » selon les instructions utilisées, et cela peut donc avoir une incidence sur la gestion de la valeur par le circuit.

Une manière de mesurer cette différence est d'utiliser des processus non « ralentis » par le CRTC et le GATE ARRAY, comme l'affichage de la HSYNC par exemple. Voir chapitre 15, page 93.

On peut aussi mesurer cette différence, par exemple, entre ce qui se produit avec une I/O sur le 3<sup>ème</sup> NOP d'un OUT(C),R8 et le 5<sup>ème</sup> NOP d'un OUTI sur un CRTC 1. Voir chapitre 0, page 80.

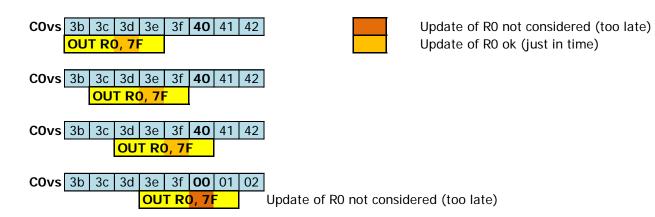

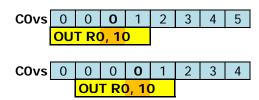

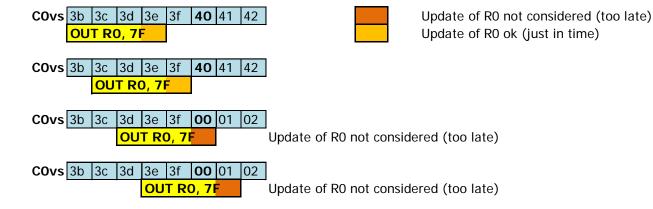

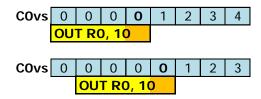

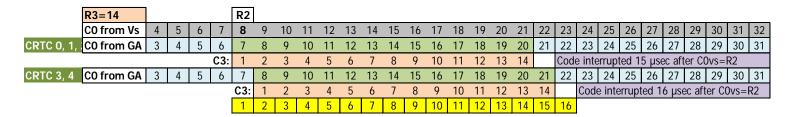

Il faut aussi noter que les CRTC 3 et 4 retardent la mise à jour des registres de 1  $\mu$ sec. Il faut donc que ces instructions surviennent 1  $\mu$ sec plus tôt que sur un CRTC 0, 1 ou 2.

Par convention dans ce document, j'ai considéré pour les CRTC 3 et 4, que l'entrée sortie avait lieu 1 µsec plus tard dans l'instruction afin de simplifier les schémas et la compréhension générale.

En pratique, cela impose donc, pour un code réalisé sur CRTC 3 ou 4, de positionner l'instruction d'entrée-sortie 1 µsec avant celle qu'on aurait placée pour un CRTC 0, 1 ou 2.

Ceci est dit!

## **5 LES AUTRES CIRCUITS**

## 5.1ACCÈS

Les périphériques, sur CPC, ont été câblés de manière à décoder partiellement l'adresse utilisée pour effectuer l'entrée/sortie. (ai-je déjà écrit « Bienvenue sur CPC » ?).

Un périphérique est concerné par une opération d'entrée/sortie dès que quelques bits précis du bus d'adresse sont positionnés à 0 et/ou 1. Ce qui implique que si d'autres bits relatifs à d'autres périphériques sont également positionnés, alors l'opération d'entrée/sortie va également les concerner.

Il est donc possible d'envoyer une même valeur à différents périphériques **simultanément**.

L'intérêt peut sembler relatif car les valeurs communes utiles à plusieurs périphériques ne sont pas énormes. Cependant, si on mesure bien les conséquences d'envoyer des valeurs imprévues à un périphérique, cela permet de faire des « économies » de registre(s) en modifiant judicieusement la valeur des registres Z80A B et/ou C.

Dans un environnement hautement contraint par le temps machine, cela peut avoir l'intérêt d'affecter d'autres usages à ces registres.

|                    |     | Re | egi | st | er | В  | (or | Α | ) |   | R   | eg | jis <sup>.</sup> | te | r (     | C ( | or | · n | )           |       |  |  |  |  |  |

|--------------------|-----|----|-----|----|----|----|-----|---|---|---|-----|----|------------------|----|---------|-----|----|-----|-------------|-------|--|--|--|--|--|

| Circuit            | 15  | 14 | 13  | 12 | 11 | 10 | 9   | 8 |   | 7 | 6   | 5  | 4                | 3  | 2       | 1   | О  |     | Select Addr |       |  |  |  |  |  |

| PAL                | W   | 0  | Х   | Х  | Х  | Х  | Х   | Х | Х | 2 | Х   | Х  | Х                | Х  | Х       | Х   | Х  | Х   |             | &7F00 |  |  |  |  |  |

| Gate Array         | W   | 0  | 1   | Х  | Х  | Х  | Х   | х | Х |   | Х   | Х  | Х                | Х  | Х       | Х   | Х  | х   |             | &7F00 |  |  |  |  |  |

| CRTC Select        | W   | Х  | 0   | Х  | Х  | Х  | Х   | 0 | 0 |   | Χ   | Х  | Х                | Х  | Х       | Х   | Х  | Х   |             | &BC00 |  |  |  |  |  |

| CRTC Write         | W   | Х  | 0   | Х  | Х  | Х  | Х   | 0 | 1 |   | Χ   | Х  | Х                | Х  | Х       | Х   | х  | Х   |             | &BD00 |  |  |  |  |  |

| <b>CRTC Status</b> | r   | Х  | 0   | Х  | Х  | Х  | Х   | 1 | 0 |   | Х   | Х  | Х                | Χ  | Χ       | Х   | Х  | Х   |             | &BE00 |  |  |  |  |  |

| CRTC Read          | r   | Х  | 0   | Х  | Х  | Х  | Х   | 1 | 1 | 2 | Х   | Х  | Χ                | Х  | x       |     |    |     |             | &BF00 |  |  |  |  |  |

| ROM Select         | W   | Х  | Х   | 0  | Х  | Х  | Х   | х | Х |   | Х   | Х  | Х                | Х  | Х       | Х   | х  | Х   |             | &DF00 |  |  |  |  |  |

| Printer            | W   | Х  | Х   | Х  | 0  | Х  | Х   | х | Х |   | Х   | Х  | Х                | Х  | Х       | Х   | х  | Х   |             | &EF00 |  |  |  |  |  |

| PPI Port A         | r/w | Х  | Х   | Х  | Х  | 0  | Х   | 0 | 0 | 2 | Х   | Х  | Х                | Х  | Х       | Х   | х  | Х   |             | &F400 |  |  |  |  |  |

| PPI Port B         | r/w | Х  | Х   | Х  | Х  | 0  | Х   | 0 | 1 |   | Χ   | Х  | Х                | Х  | Х       | Х   | Х  | Х   |             | &F500 |  |  |  |  |  |

| PPI Port C         | r/w | Х  | Х   | Х  | Х  | 0  | Х   | 1 | 0 |   | Х   | Х  | Х                | Х  | Х       | Х   | Х  | Х   |             | &F600 |  |  |  |  |  |

| PPI Control        | W   | Х  | Χ   | Х  | Х  | 0  | Х   | 1 | 1 |   | Χ   | Х  | Χ                | Х  | Х       | Х   | Х  | Х   |             | &F700 |  |  |  |  |  |

| FDC Status         | r   | Х  | Х   | Х  | Х  | Х  | 0   | Х | 1 |   | O X |    | Х                | Х  | Х       | Х   | Х  | 0   |             | &FB7E |  |  |  |  |  |

| FDC Data           | r/w | Х  | Х   | Х  | Х  | Х  | 0   | Х | 1 |   | 0   | Х  | Х                | Χ  | x x x x |     | 1  |     | &FB7F       |       |  |  |  |  |  |

| FDC Motor          | W   | Х  | Х   | Χ  | Х  | Х  | 0   | Х | 0 |   | 0   | Х  | Х                | Χ  | Χ       | Χ   | Х  | Х   |             | &FA7F |  |  |  |  |  |

Enfin, toujours dans la perspective d'environnements contraints, il peut être utile de considérer que tous les bits d'une valeur envoyée à un périphérique ne sont pas utiles.

Pour un CRTC, c'est vrai pour une donnée de mise à jour d'un registre, comme R9 tronqué à 5 bits, tout comme la valeur du numéro de registre.

Autrement dit, on peut sélectionner R9 avec la valeur 9, mais aussi &31 (00110001), et le mettre à jour avec la valeur 7, mais aussi &27 (00100111).

## 5.2 CPC + / GX 4000

Sur l'AMSTRAD PLUS, il est possible de communiquer directement avec le CRTC émulé, via des registres complémentaires créés spécifiquement pour gérer les fonctions complémentaires "PLUS". Ces fonctions permettent par exemple de faire des masquages de données, d'effectuer des décalages fins, de définir des lignes et adresses de rupture, ou même de caler une interruption raster ou "dma" (non sans bug toutefois).

L'objectif actuel de ce document n'est pas (encore) d'analyser l'interaction entre ces registres et l'émulation faite du CRTC. L'accès à ces registres spécifiques ne passe pas par le système d'entrée/sortie du Z80A décrit précédemment.

L'AMSTRAD PLUS dispose d'une page de registres dit "mappés" sur une adresse. Chaque registre dispose donc de sa propre adresse.

Le Z80A accède à ces registres avec de simples écritures (ou lecture) à une adresse donnée.

Il est donc possible d'accéder à certaines fonctions (par exemple la modification d'une couleur) de deux manières différentes. Les informations indiquées pour le CRTC 3 dans cette version du document concernent uniquement des I/O réalisées via les instructions OUT du Z80A.

A noter cependant que la page de ces registres, située entre &4000 et &7FFF, est accessible via une fonction jusqu'alors inexploitée du GATE ARRAY.

Cette fonction est cependant elle-même conditionnée à l'utilisation d'une séquence de « déverrouillage » de 17 octets qui doit être envoyée sur le port de sélection (&BC00) du CRTC.

255, 0, 255, 119, 179, 81, 168, 212, 98, 57, 156, 70, 43, 21, 138, 205, 238

#### Remarque:

Il ne sert à rien d'envoyer cette séquence sur un CRTC 4.

Ils n'ont pas utilisé la même séguence.

Je ne dirais rien de plus sans la présence de mon avocat...

# 6 CONSTRUCTION D'UN ÉCRAN

## **6.1LOGIQUE GENERALE**

Les algorithmes suivants décrivent la logique générale de gestion d'affichage avec un CRTC « idéal ». Nous le verrons plus loin, cette logique est parfois très différente selon les situations.

#### **6.1.1 COMPTAGE DES CARACTERES**

C0 est incrémenté

Lorsque C0 atteint R0

C0 passe à 0

C9 est incrémenté

Lorsque C9 atteint R9

C9 passe à 0

C4 est incrémenté

Lorsque C4 atteint R4

Lorsque C5 atteint R5

C4 passe à 0, C5 passe à 0

MA est rechargé à partir de R12/R13

Sinon C5 est incrémenté

#### 6.1.2 SYNCHRONISATIONS

Lorsque C0 atteint R2

Hsync débute, C3h=0

C3h est incrémenté si R3h>0

Lorsque C3h=R3h

Fin de Hsync

Lorsque C4 atteint R7

Vsync débute, C3v=0

C3v est incrémenté

Lorsque C3v atteint R3v (ou 16)

Fin de Vsync

#### **6.1.3 AFFICHAGE DES CARACTERES**

Lorsque C0 passe à 0 L'affichage des caractères est activé Lorsque C0 atteint R1 L'affichage des caractères est désactivé

Lorsque C4 passe à 0 L'affichage des lignes de caractères est activé Lorsque C4 atteint R6 L'affichage des lignes de caractères est désactivé

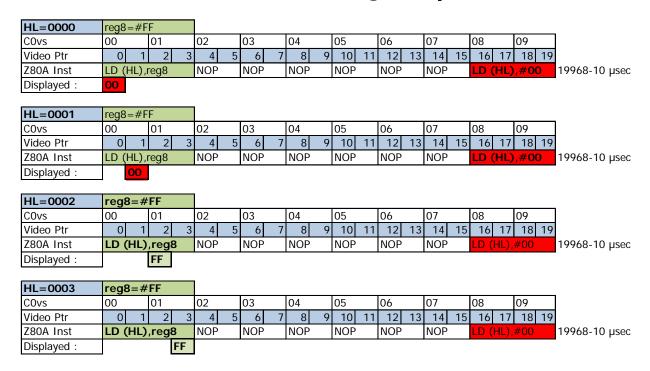

#### **6.1.4 POINTEUR VIDEO**

A chaque µsec, VMA est incrémenté de 2 tant que l'affichage est actif et C9 intervient dans l'adresse

Si C0=R0 alors C0=0 vrai pour R0=0 vrai pour R9=0 Si C9=R9 Alors C9=0 vrai pour R9=0 Si C4=R4 alors Si R5=0 alors vrai pour R5=0 vrai pour R4=0

$$MA=R12/R13$$

Sinon C4=C4+1 (crtc 0, 1, 2) et Gestion C5

$\begin{array}{c} \text{Sinon C4=C4+1} \\ \text{Sinon C9=C9+1} \\ \text{sinon C0=C0+1} \end{array}$

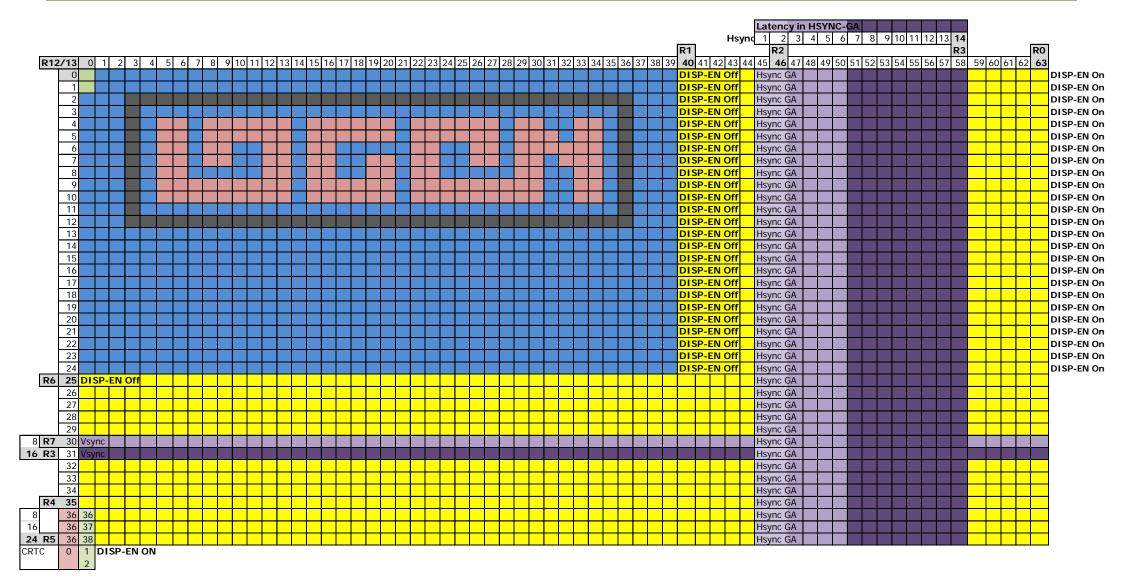

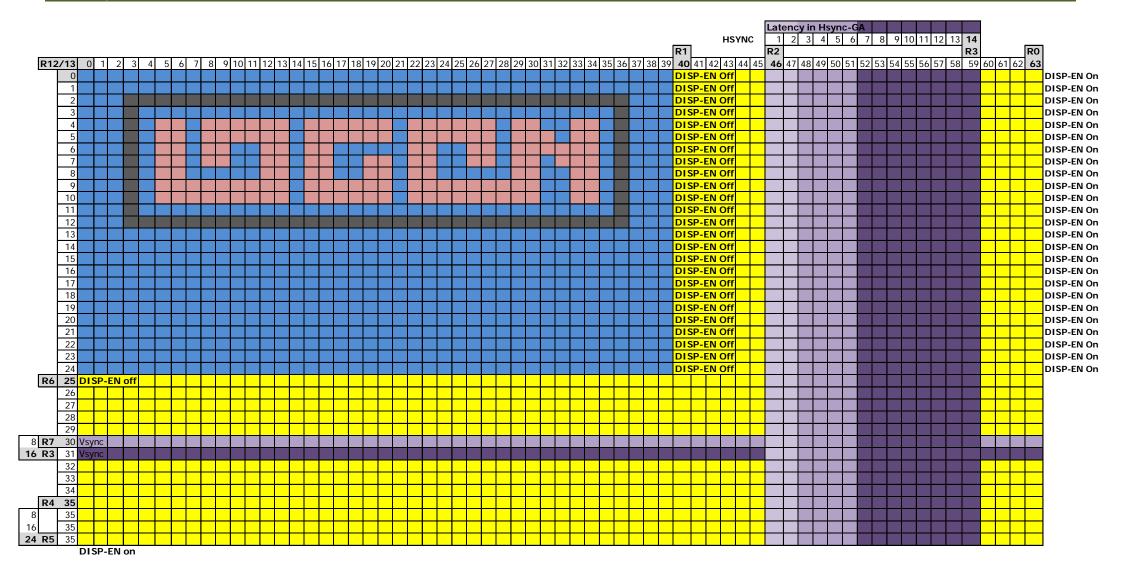

#### 6.1.5 REPRÉSENTATION SCHÉMATIQUE

Les schémas suivants décrivent globalement la construction d'un écran à partir des différents registres, sans que les registres soient modifiés durant le balayage.

| <b>Définition Ecran</b> | Hoi                     | riz. I   | Reg |    | Vertical Reg |    |    |    |    |  | Vid P | tr | Special |

|-------------------------|-------------------------|----------|-----|----|--------------|----|----|----|----|--|-------|----|---------|

|                         | R0                      | R1       | R2  | R3 | R4           | R5 | R6 | R7 | R9 |  | R12/R | 13 | R8      |

|                         | 63 40 46 14 35 24 25 30 |          | 7   |    | &30          | 0  | 0  |    |    |  |       |    |         |

| (DO 4) E((D4 4          |                         | <u> </u> | 411 |    | <br>         |    |    |    |    |  |       |    |         |

$$(R0+1) \times [((R4+1) \times (R9+1)) + R5]$$

64 x  $((36 \times 8)+24) = 19968 \mu s$

Description des 16 premières lignes en vert indiquées sur les schémas pages suivantes :

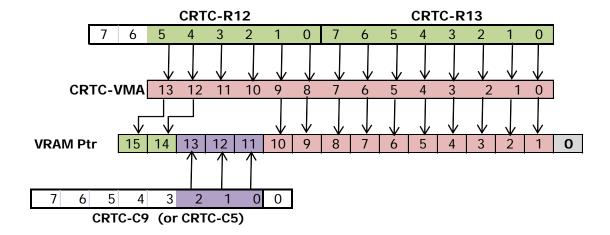

| Vic | leo | Poin | ter |    |    |     |   |   |   |   |   |   |   |   |   |      |    |    |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   |    |

|-----|-----|------|-----|----|----|-----|---|---|---|---|---|---|---|---|---|------|----|----|-----|------|-----|---|---|---|---|---|----|-----|------|-----|---|---|---|---|----|

| #   | 14  | 13   | 12  | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |      |    |    |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | _  |

| R1  | 2   | C9   | (*) |    | R1 | 2/1 | 3 |   |   |   |   |   |   |   | 0 | Hex  |    |    | Fir | st k | yte | ÷ |   |   |   |   | Se | con | ıd k | yte |   |   |   |   |    |

| 5   | 4   | 2    | 1   | 0  | 9  | 8   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 0 | Addr |    | C9 | 7   | 6    | 5   | 4 | 3 | 2 | 1 | 0 | 7  | 6   | 5    | 4   | 3 | 2 | 1 | 0 | C4 |

| 1   | 1   | 0    | 0   | 0  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | C000 |    | 0  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 0    | 0   | 1  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | C800 |    | 1  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 0    | 1   | 0  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D000 |    | 2  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 0    | 1   | 1  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D800 |    | 3  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 1    | 0   | 0  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | E000 |    | 4  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 1    | 0   | 1  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | E800 |    | 5  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 1    | 1   | 0  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | F000 |    | 6  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 1    | 1   | 1  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | F800 | R9 | 7  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 0  |

| 1   | 1   | 0    | 0   | 0  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | C050 |    | 0  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 0    | 0   | 1  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | C850 |    | 1  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 0    | 1   | 0  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | D050 |    | 2  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 0    | 1   | 1  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | D850 |    | 3  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 1    | 0   | 0  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | E050 |    | 4  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 1    | 0   | 1  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | E850 |    | 5  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 1    | 1   | 0  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | F050 |    | 6  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

| 1   | 1   | 1    | 1   | 1  | 0  | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | F850 | R9 | 7  |     |      |     |   |   |   |   |   |    |     |      |     |   |   |   |   | 1  |

(\*) C5 on CRTC 3, 4 in vertical adjustment period (R5)

## 7 SYNCHRONISATION

## 7.1PRINCIPES

Le CRTC est chargé de déterminer les adresses mémoire à afficher, qu'il communique au GATE ARRAY, qui lit les données et les gère selon ses paramètres, pour générer des pixels plus ou moins larges et colorés.

Le CRTC envoie aussi au GATE ARRAY les signaux VSYNC et HSYNC, que ce dernier recombine pour envoyer un signal composite au moniteur.

- Lorsque le GATE ARRAY reçoit un signal HSYNC, il y a 2 µs de latence avant que la "vraie" synchro horizontale du moniteur débute.

- Lorsque le GATE ARRAY reçoit un signal VSYNC, il y a 2 lignes de latence avant que la "vraie" synchro verticale du moniteur débute.

Sur un sujet qui traite des différences entre des modèles de circuits à l'échelle de la microseconde, il est important de spatialiser les instructions par rapport à ce qui est affiché.

Plusieurs difficultés sont liées à cette démarche :

- Situer une instruction Z80A par rapport au fonctionnement interne du CRTC, dans la mesure où des délais peuvent exister entre la mise à jour des registres internes et le moment où les caractères sont affichés.

- Déterminer quand, durant l'instruction d'entrée sortie, la modification d'un registre CRTC est effective et prise en compte.

Le même type de question existe pour les instructions Z80A accédant directement au GATE ARRAY, ou lors de la mise à jour de la RAM lue par le GATE ARRAY.

Pour « spatialiser » les instructions, ce document se base sur un point de référence unique sur lequel sont alignées les instructions en Z80A affectant la vidéo.

Ce point de référence est le moment ou on considère que C0=0 au sens CRTC.

Il existe un différé d'affichage entre le moment ou le CRTC fournit un pointeur vidéo, et le moment ou le GATE ARRAY affiche le caractère 16 bits correspondant. Ce différé est de 1 µsec.

Ce décalage temporel d'affichage du GATE ARRAY par rapport au CRTC ne serait pas gênant si l'intégralité de ce qui est envoyé par le CRTC au GATE ARRAY était **toujours** retardé de 1 µsec.

Mais ce n'est pas toujours le cas, en particulier pour la gestion du signal HSYNC pour les machines équipées des CRTC 0, 1 et 2.

Lorsque ce document traite d'instructions Z80A, et que leur spatialisation a une importance au regard des différences de délai, le compteur C0 est présenté sur 2 "time-line".

Celle au regard de C0 à partir du point de référence CRTC et celle au regard de l'affichage (pixels, ...) par le GATE ARRAY.

Il sera donc question de "CO from Vsync" (ou COvs) et/ou "CO from GA" lorsque l'affectation des registres du CRTC est déterminante par rapport à l'affichage des caractères par le GATE ARRAY.

Le CRTC communique avec le Z80A de deux manières différentes (en dehors des registres en lecture ou du registre de statut du CRTC 1) :

- Soit via la broche VSYNC du CRTC qui est reliée directement au bit 0 du port B du PPI 8255.

- Soit via les interruptions du Z80A produites par le GATE ARRAY à partir des signaux HSYNC du CRTC.

#### 7.2 SYNCHRONISATION VSYNC

Le CRTC génère un signal sur sa broche VSYNC une µsec avant que C4=R7 et que C0 passe à 0. C'est un indicateur fiable pour baser ensuite toute autre méthode de synchronisation.

Le bit 0 du port B du PPI (adresse d'entrée sortie "standard" &F5) passe à 1 dès que le signal VSYNC est produit par le CRTC.

En général, les programmes font des "boucles" pour attendre que ce bit passe à 1, ce qui entraine une marge d'erreur liée à la durée des instructions du code d'attente.

Cette marge existe même si le code de « boucles » est "aligné" grâce à une interruption générée à partir d'une instruction HALT située avant la boucle d'attente (la marge est juste "stable").

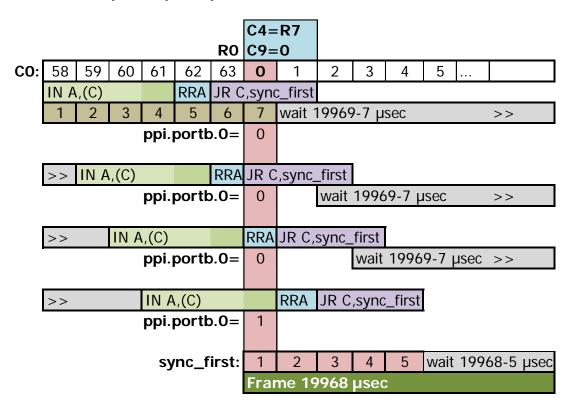

Il est cependant parfaitement possible d'écrire un code capable de caler du code Z80A sur la microseconde qui correspond à C4=R7 et C0=C9=0.

Toutes les données indiquées dans ce document utiliseront ce point de référence **COvs**. Il est bien sûr possible d'utiliser le système d'interruption comme nouveau point de référence. Le chapitre 25.6.6 sur les interruptions fait une synthèse selon les différents CRTC.

Il ne faut en effet pas perdre de vue que les interruptions sont dépendantes des différences avec les couples CRTC/GATE ARRAY des différentes machines.

Le principe du code de synchronisation **COvs** est de placer une attente de VSYNC dans une période ou l'indicateur au niveau du PPI n'est pas encore positionné à 1.

Il s'agit ensuite de faire dériver ce code microseconde par microseconde à chaque frame, grâce à une période de **19969** microsecondes. Ce balayage est plus long de 1 microseconde que celui produit par le CRTC (avec une programmation adéquate et standard de 312 lignes de 64µsec).

Ceci peut être vu comme une "dérive" du code microseconde par microseconde.

L'instruction d'entrée sortie, qui lit le port B du PPI, est l'instruction IN A,(C) et s'exécute en 4 µsec.

C'est sur la 4ème µsec de l'instruction IN A,(C) que A est mis à jour lorsque le bit 0 du port B passe à 1. Le point de référence **COvs** est calculé de cette manière toutes les informations indiquées dans ce document sont corrélées à cette mesure, qui est un point de référence unique.

#### Description schématique du principe :

#### Code de synchronisation :

```

Synchronisation Vsync

```

A l'issue du call de synchronisation, la 1ere usec est celle sur laquelle le CRTC a positionné le signal Vsync Principe

- attendre le signal vsync avec la marge d'erreur

```

- attendre que le signal vsync se termine

- faire deriver le test de vsync avec une boucle durant 19968+1 us

- des que la vsync est detectee par le test, c'est la detection au plus tot, a laquelle il faut soustraire la duree du test

sync_vbl

ld b,#f5

; Attendre flag VBL =1

ld hl,19968-23

; Compteur de nop (moins les marges et la gestion de l'attente)

Id de,-11

; Ici on attend le debut de la periode VBL (ou on attend pas si on y etait deja)

sync_wvblon1

in a,(c)

rra

jr nc,sync_wvblon1

; Flag Vsync CRT passe a 1 (ou etait deja a 1)

sync_wvbloff1

in a,(c)

; Attendre que le flag repasse a 0 (Fin de Vsync)

rra

jr c,sync_wvbloff1

; On est certain maintenant que le signal Vsync n'etait pas deja en cours

sync_wvblon2

in a,(c)

; marge1 de 7us

rra

jr nc,sync_wvblon2

sync_wvbloff2

Attendre que le signal Vsync repasse a 0 en comptant le temps ecoule

add hl.de

3

On nop2

On nop3

in a,(c)

; 4

2

1

1

rra

1

jr c,sync_wvbloff2

(bcl)+3+4+1+2=15 / marge 15-5=10

; 3/2

2

3

ex de,hl

1

; 5 >> 6 + 10(marge2)

call wait_usec

; Zone de derive pour attendre de nouveau la premiere manifestation du flag

; le in a,(c) va "descendre" nop par nop (frame par frame) jusqu'a ce que le in recupere le flag actif

sync_derive_bcl

ld b,#f5

; 2

```

```

; 1 usec (+1)

rra

jr c,sync_first

; 2/3 (+3)

ld de,19969-20

; 3

; 5+(19969-20)

call wait_usec

jr sync_derive_bcl

; 3 >> 20

sync_first

; 6 Le flag a ete détecté au plus tôt, et ce depuis 5 usec (2+1+3) C0=R0

; -1 µs pour se positionner sur C0=0

ld de,19968-11

; 3

; 3 >> 11 >> de=19968-11

jp wait_usec

; wait "de" usec